計算機をはじめとする 情報機器や情報システムの更なる高性能化、低コスト化、小型化、低消費電力化を目指し、 集積回路や集積回路上に構成されるシステムの研究をしています。

当研究室では、集積回路の設計(集積回路へのシステムの実装)だけでなく、集積回路の性能を最大限に発揮する ためのシステムの構成方式(アーキテクチャ)や、集積回路の設計をするための設計方法論や設計支援ツールなど、 様々なテーマに取り組んでいます。

当研究室での研究活動を通じ、計算機の仕組みをより深く理解することができると共に、 ハードウェアとソフトウェア両方の実践的な力を身につけることができます。

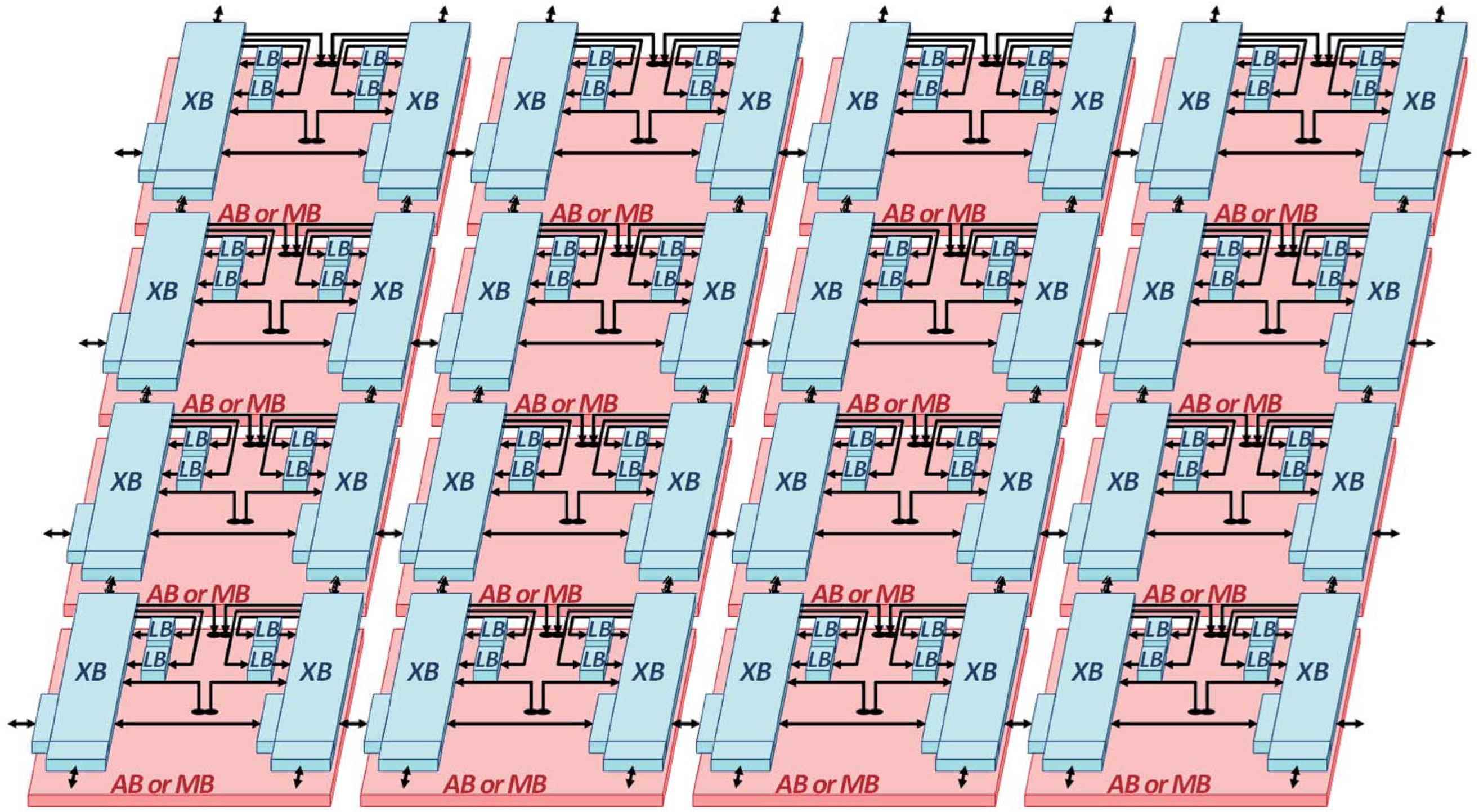

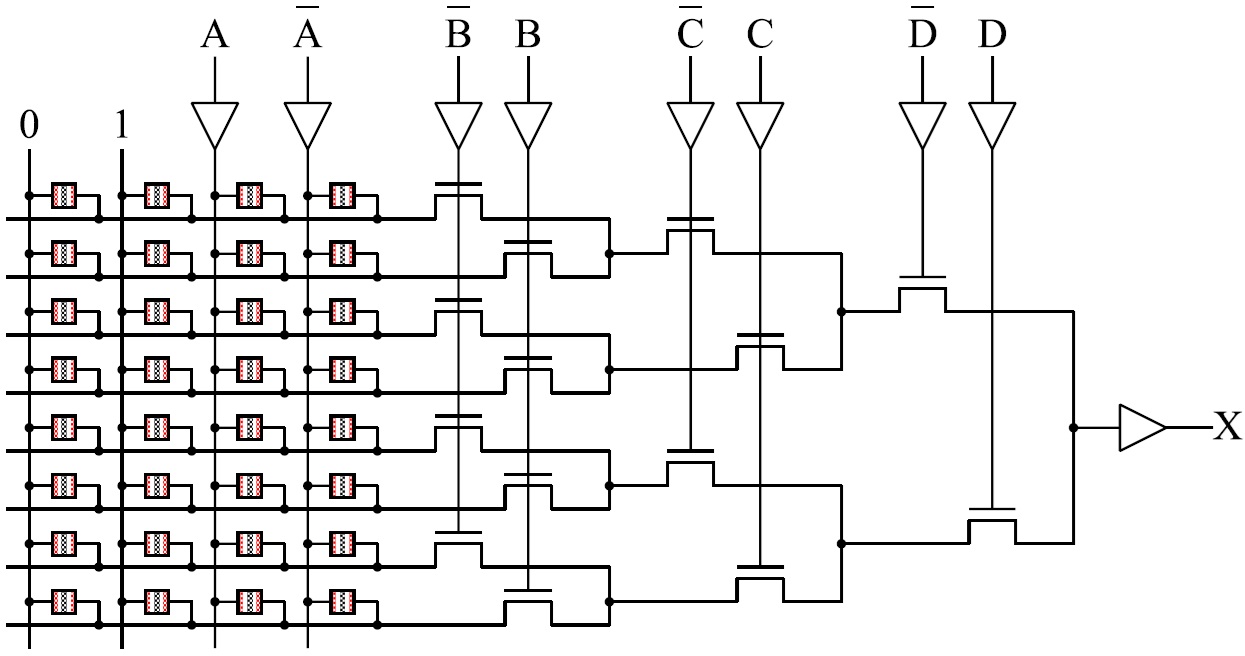

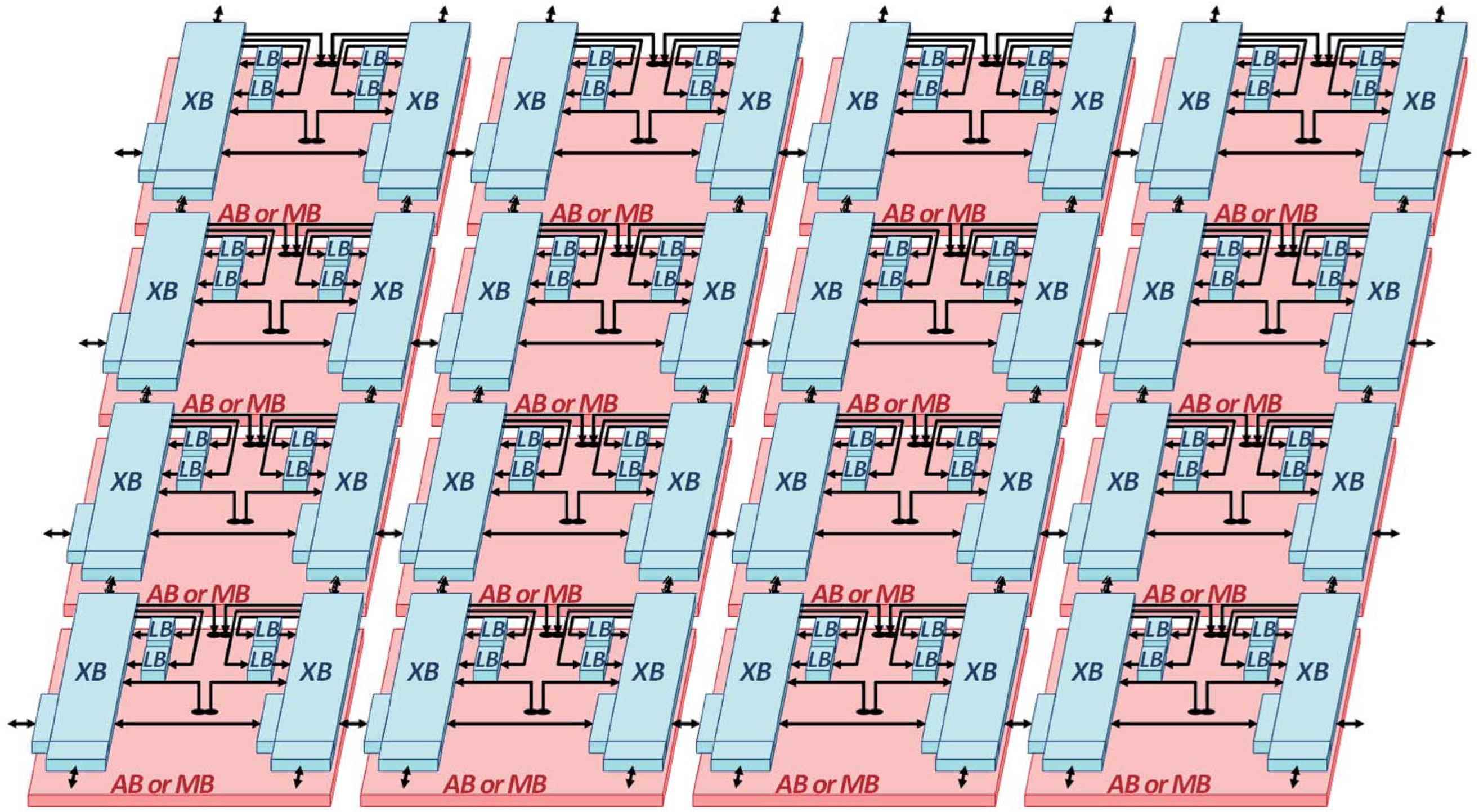

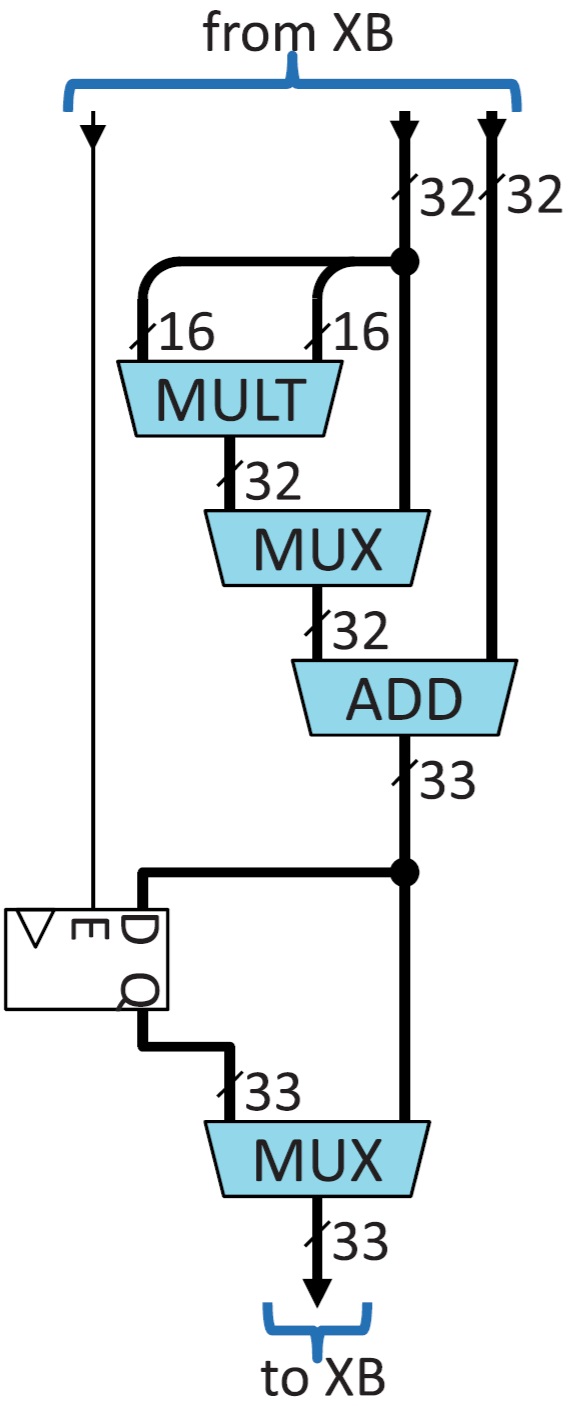

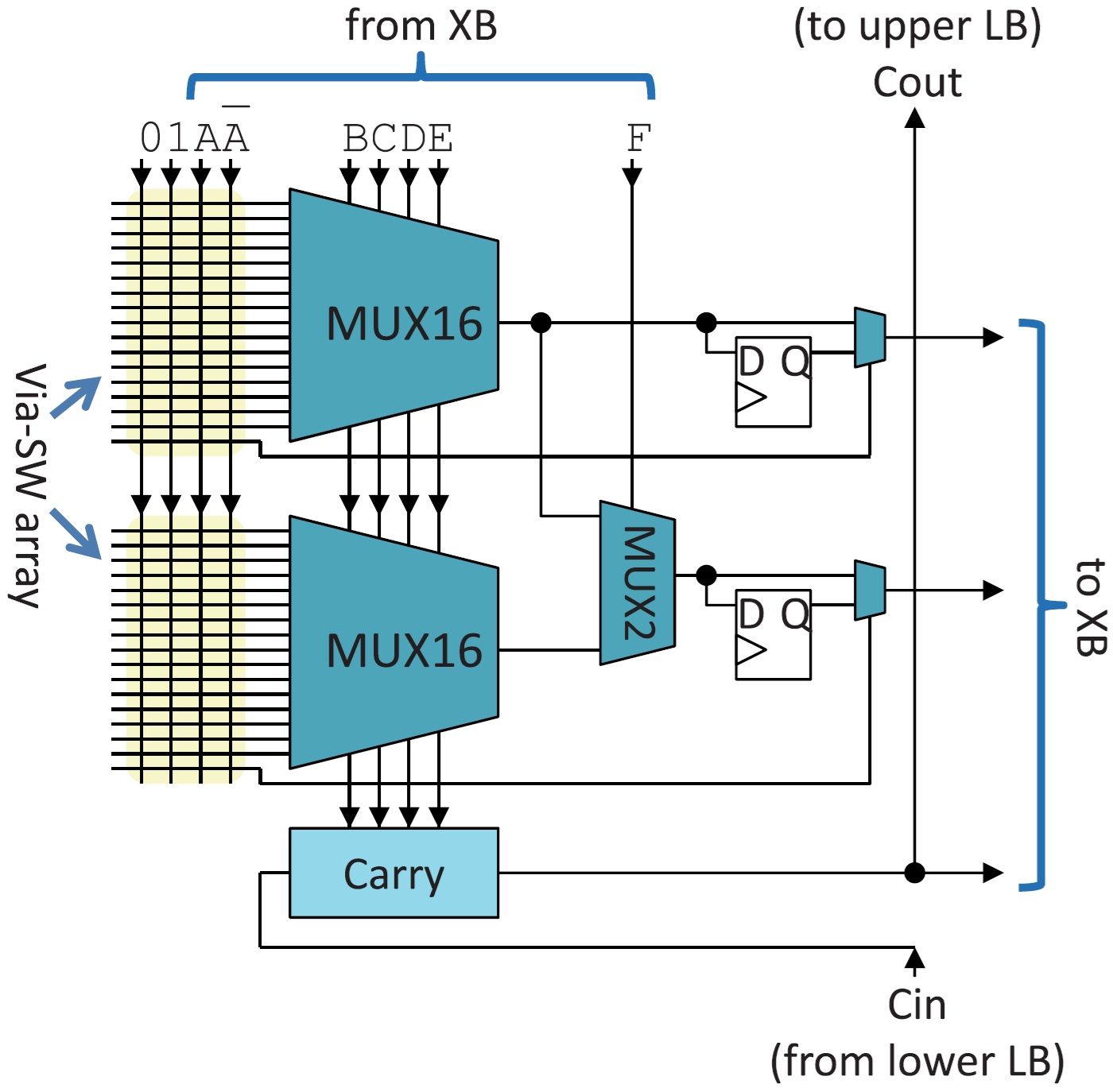

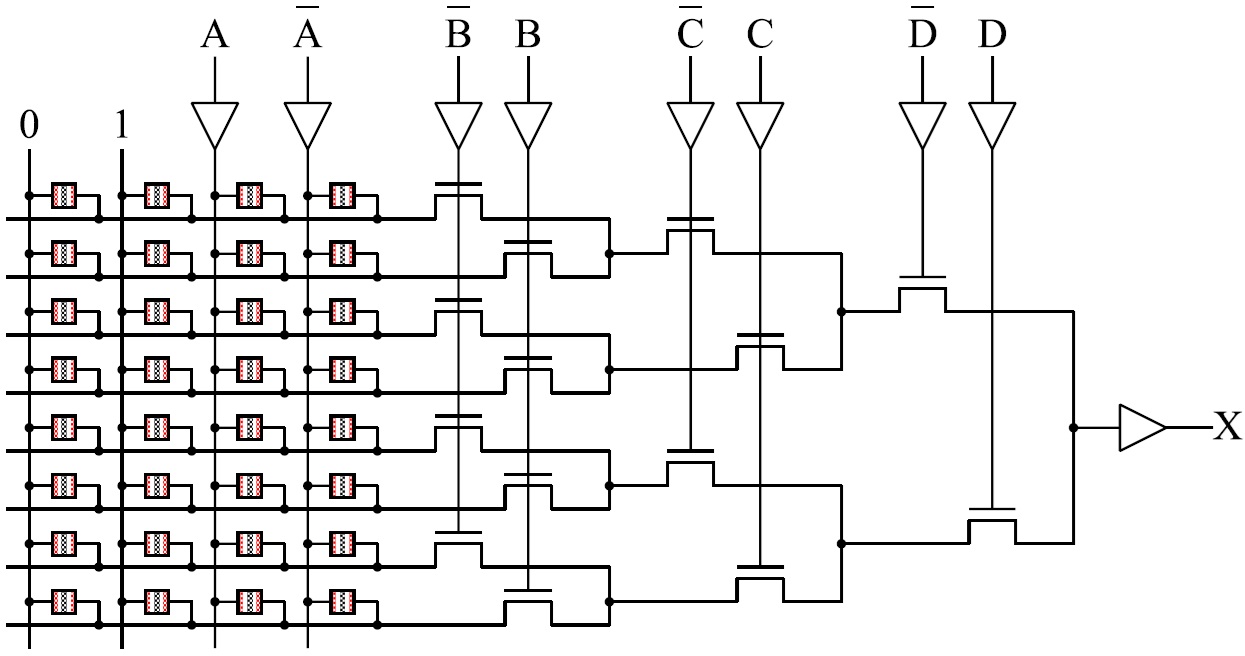

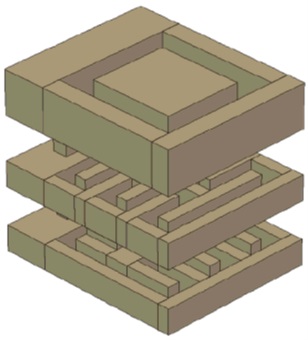

通常の集積回路は工場出荷以後に機能を変更できませんが、多様な用途を柔軟にカバーできる集積回路として、何度でも自由に機能を変更できる再構成可能デバイスが誕生しました。 その重要性は近年、画像認識などの人工知能分野で一層高まっています。 当研究室では、再構成可能デバイスのアーキテクチャ、設計ツール、応用技術などを研究しています。 特に、ビアスイッチと呼ばれる新しいナノデバイスを用いた「ビアスイッチFPGA」に関し、企業や他大学とも共同研究をしながら成果をあげています。

|

| 左より、ビアスイッチFPGAの全体構成、ロジックブロックの構成、算術ブロックの構成、0-1-A-~A-LUTの詳細 |

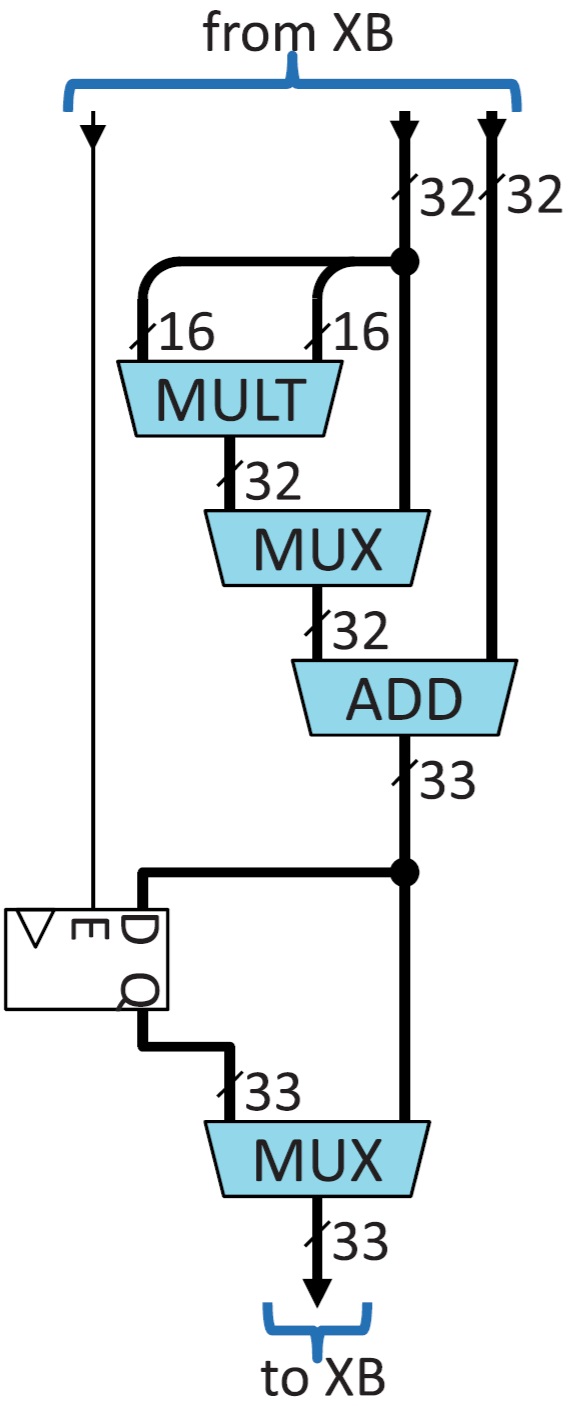

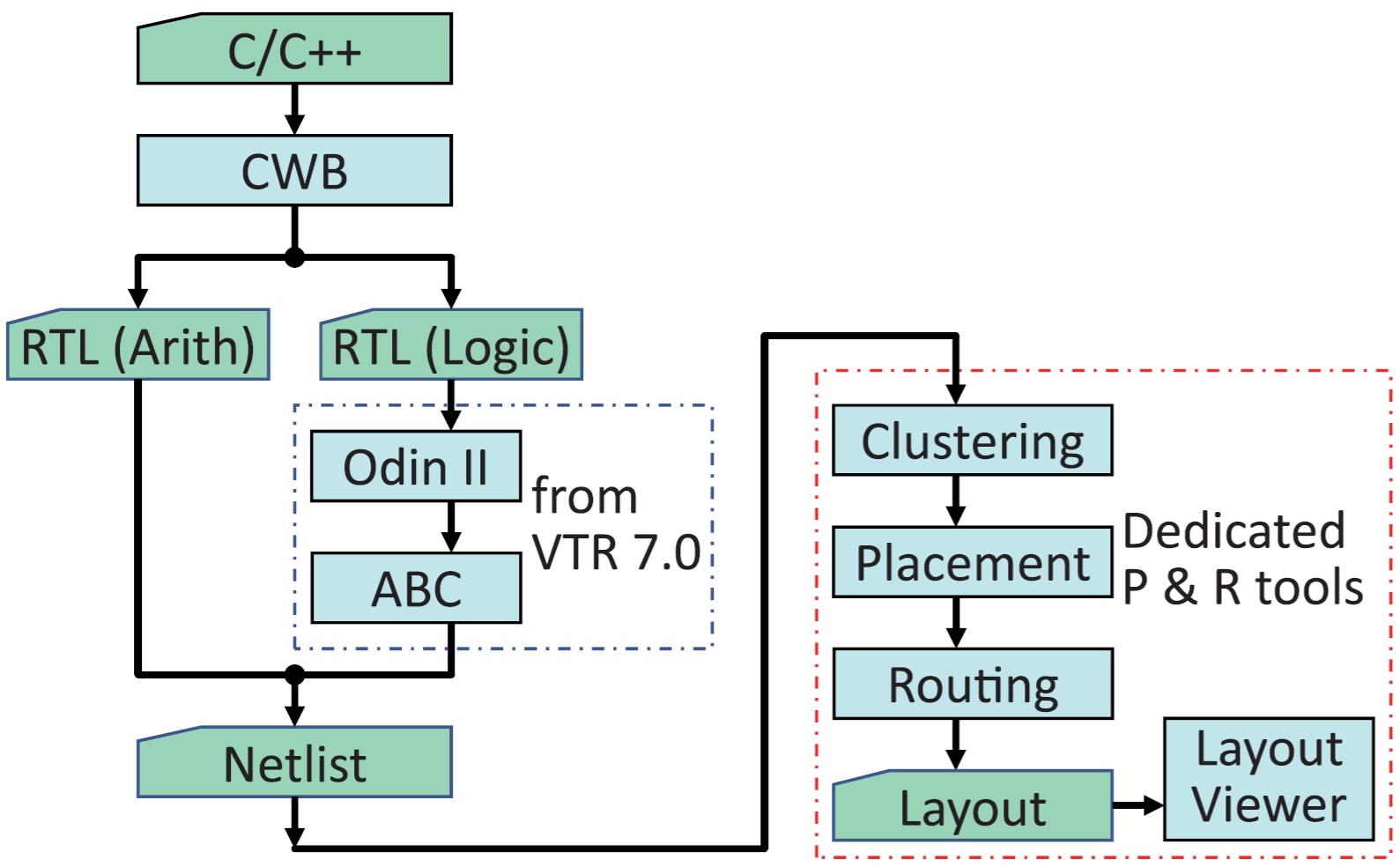

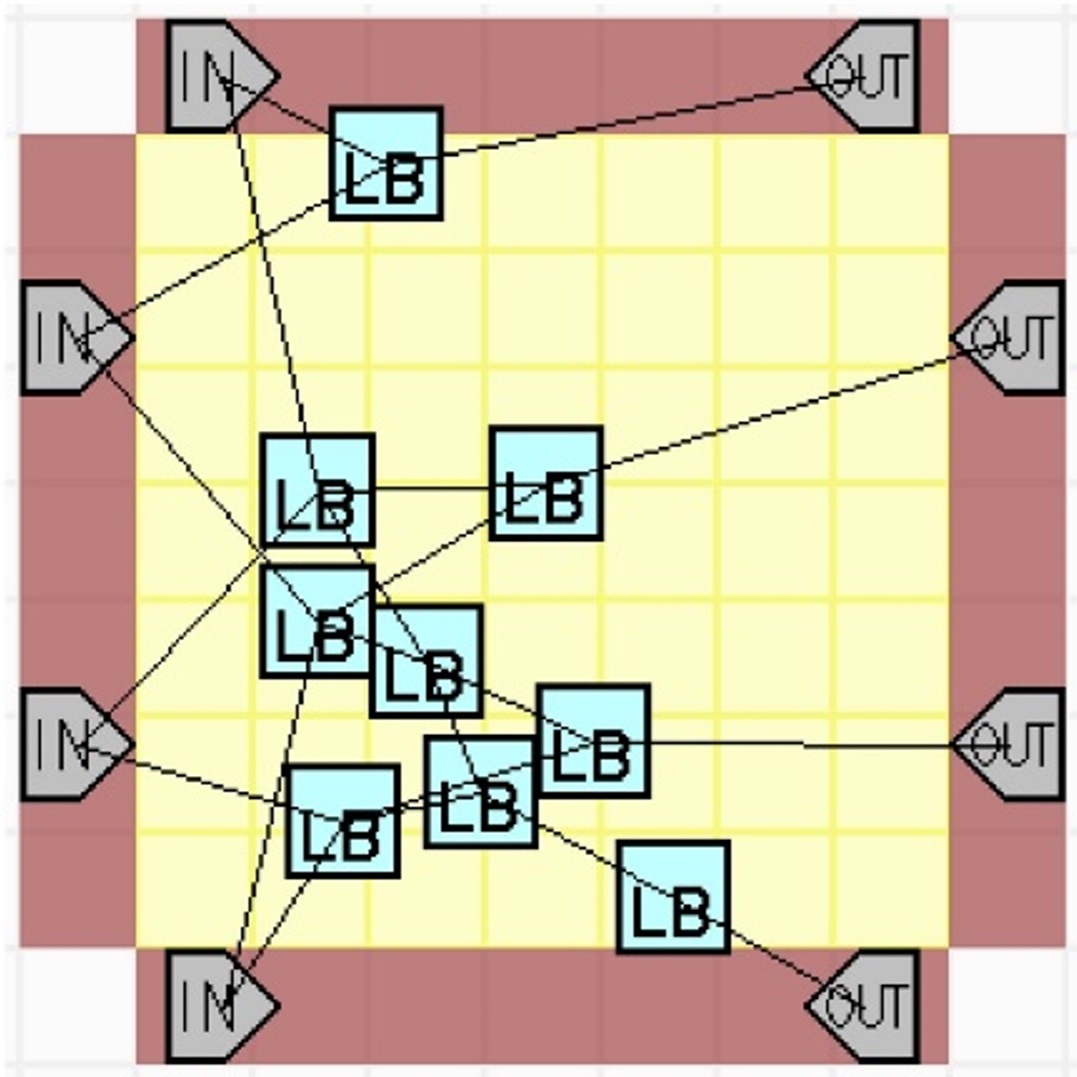

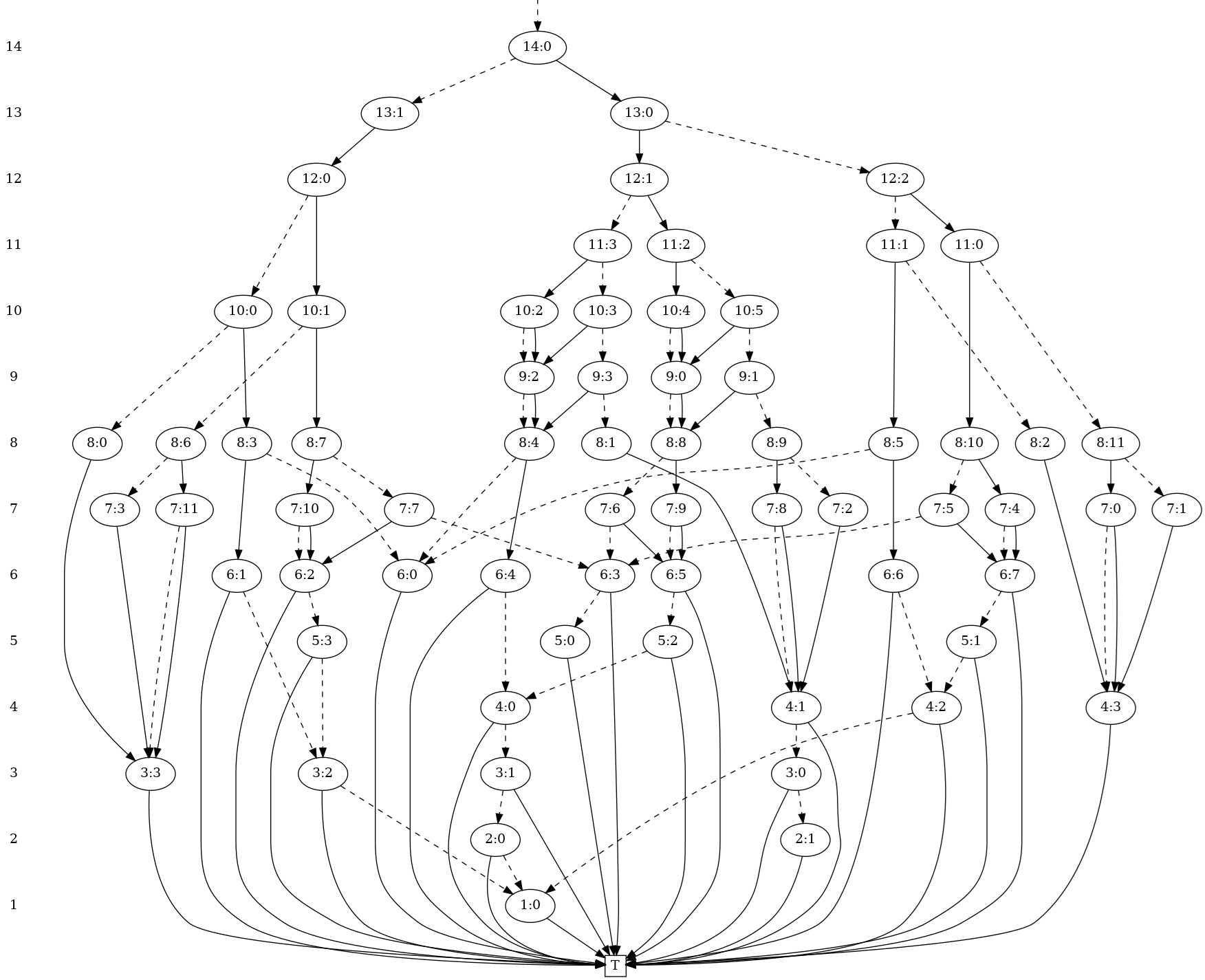

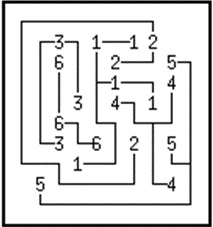

ソフトウェア開発においてコンパイラやデバッガが不可欠であるように、今日のハードウェア開発においても 設計自動化ツール(ハードウェアの設計支援を行うためのソフトウェア)が不可欠です。 特に集積回路の回路面積や消費電力を抑え、性能を最大限に引き出すためには、最適化のための優れた アルゴリズムとデータ構造が重要です。 当研究室では、再構成可能デバイス設計の上流工程から下流工程までの様々な設計自動化アルゴリズムの研究を行っています。

|

| 左より、ビアスイッチFPGAの設計フロー、自動配置の途中経過、ZDDというデータ構造で表した算術演算回路をFPGAのDSPブロックにマッピングした解の集合、集積回路の配線問題を模した多端子ナンバーリンク問題 |

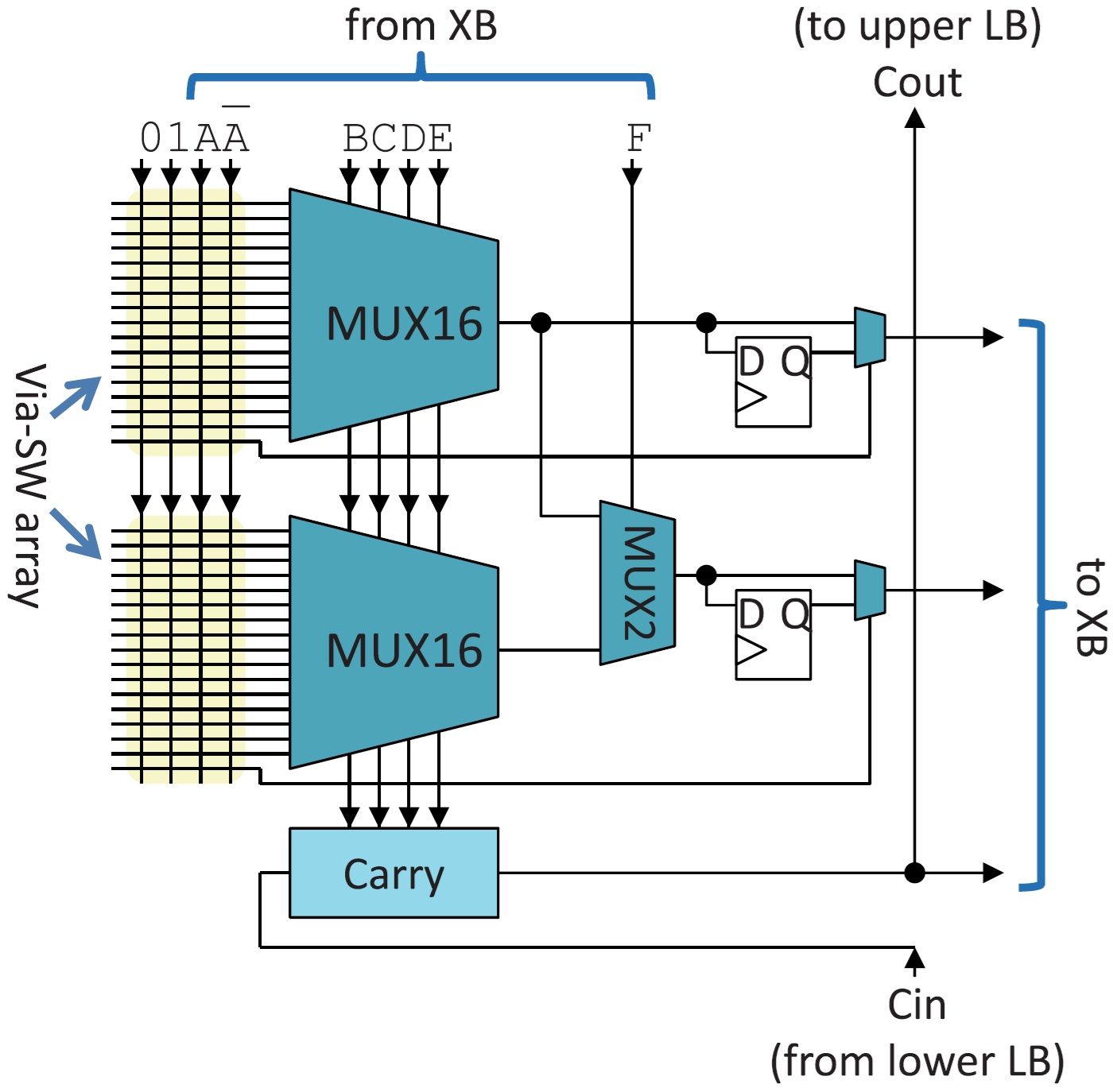

算術演算は様々な分野で需要が高い上に、集積回路上で大きな回路面積や消費電力、演算時間を要します。 例えば人工知能分野における画像認識で多用される畳み込み処理では膨大な回数の乗算が必要であり、乗算回路がシステムのコストや性能を左右します。 当研究室では、整数演算器や浮動小数点演算器、厳密演算器や近似演算器など、 様々な算術演算器のハードウェア構成(ハードウェアアーキテクチャ)およびその応用技術などを研究しています。

|

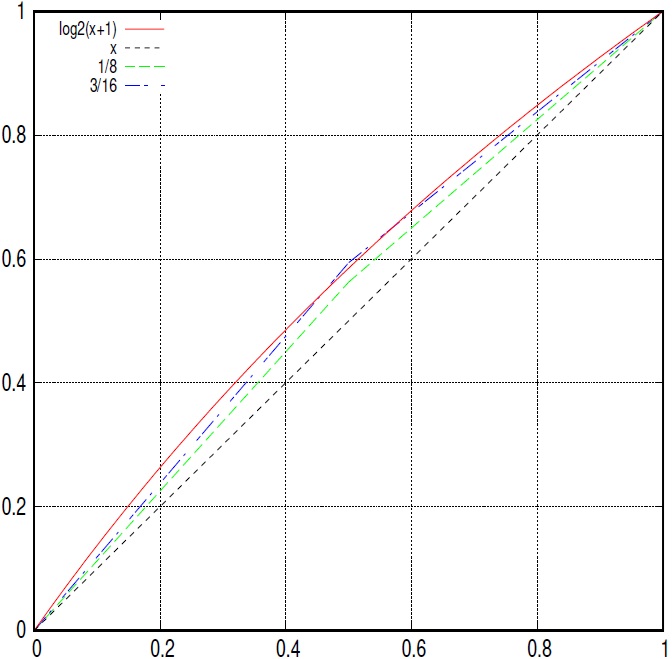

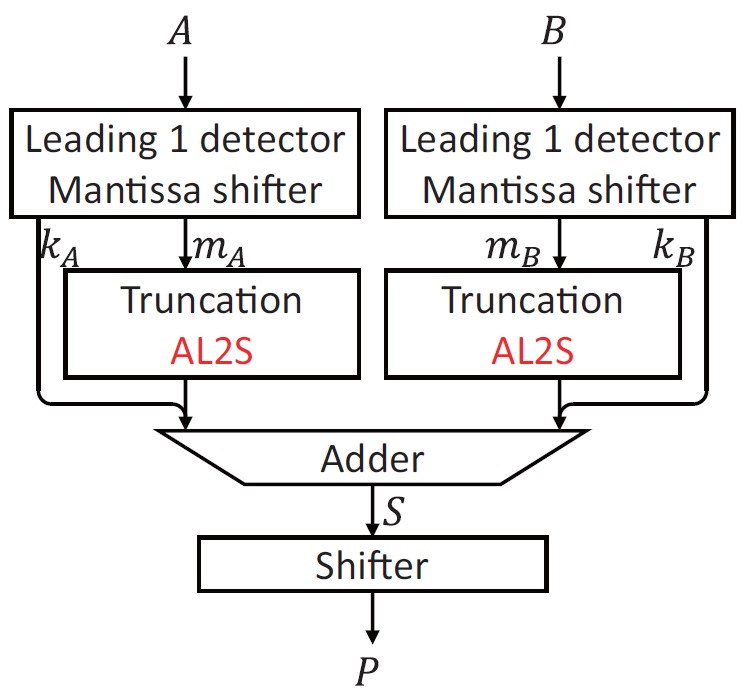

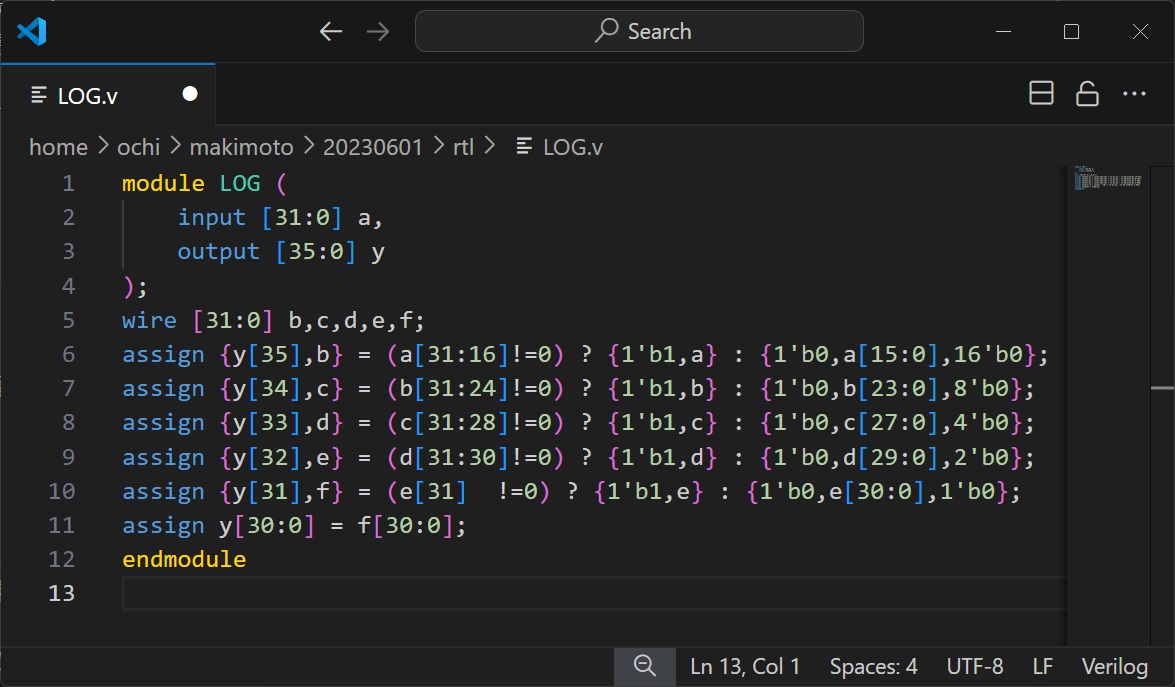

| 左より、対数関数 log2(x+1) の折れ線による近似、対数型近似乗算器hc-7のブロック図、対数変換部のVerilog-HDL記述 |

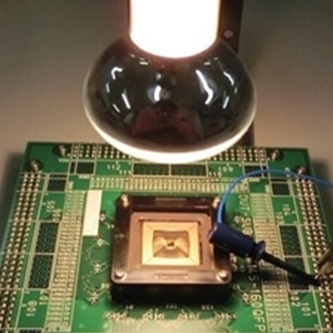

携帯電話やタブレット端末、ゲーム機に代表される携帯情報機器にはバッテリーが内蔵されており、長時間駆動のためには消費電力を極限まで低減する必要があります。 太陽電池などで電力を自給自足する小型センサーでは、更なる低消費電力化が不可欠です。 当研究室では、太陽電池などによる電源供給をも想定した回路やシステム構成の低消費電力化技術について研究しています。

|

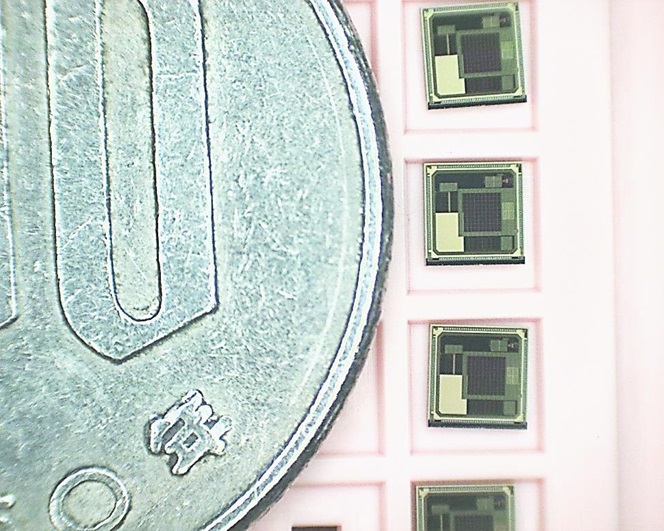

| 左より、試作した集積回路の写真(左は100円硬貨)、オンチップ太陽電池への光照射実験、不揮発性メモリに使うFishbone-in-Cage Capacitor (FiCC)の構造、オシロスコープによる波形観測、サーモカメラによるチップ温度計測 |